# S1D19105 Series

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2005, All rights reserved.

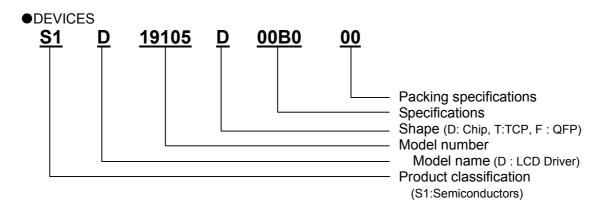

# Configuration of product number

# CONTENTS

| 1. | DESCRIPTION1 |                                                                                                                       |    |  |  |  |  |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2. | FEATURES     |                                                                                                                       |    |  |  |  |  |

| 3. | BLO          | CK DIAGRAM                                                                                                            | 3  |  |  |  |  |

| 4. | PIN /        | ASSIGNMENT                                                                                                            | 4  |  |  |  |  |

|    | 4.1          | S1D19105 Specifications of Chip                                                                                       |    |  |  |  |  |

|    | 4.2          | Bump Center Coordinates                                                                                               |    |  |  |  |  |

| 5. | PIN I        | DESCRIPTION                                                                                                           | 10 |  |  |  |  |

| •  | 5.1          | External Power Pins                                                                                                   | -  |  |  |  |  |

|    | 5.2          | Built-in Power Pins                                                                                                   | 10 |  |  |  |  |

|    | 5.3          | 1st Booster Pins                                                                                                      | 11 |  |  |  |  |

|    | 5.4          | The 2nd Booster Pins                                                                                                  | 11 |  |  |  |  |

|    | 5.5          | The 3rd Booster Pins                                                                                                  |    |  |  |  |  |

|    | 5.6          | The 4th Booster Pins                                                                                                  |    |  |  |  |  |

|    | 5.7          | Vсом Generation Pins                                                                                                  |    |  |  |  |  |

|    | 5.8          | Control Pins                                                                                                          |    |  |  |  |  |

|    | 5.9          | γ Reference Output Pin                                                                                                |    |  |  |  |  |

|    |              | RGB Interface Signal Pins                                                                                             |    |  |  |  |  |

|    |              | Test Pins                                                                                                             |    |  |  |  |  |

|    |              | Dummy Output Pins                                                                                                     |    |  |  |  |  |

| 6  |              | CTIONAL DESCRIPTION                                                                                                   |    |  |  |  |  |

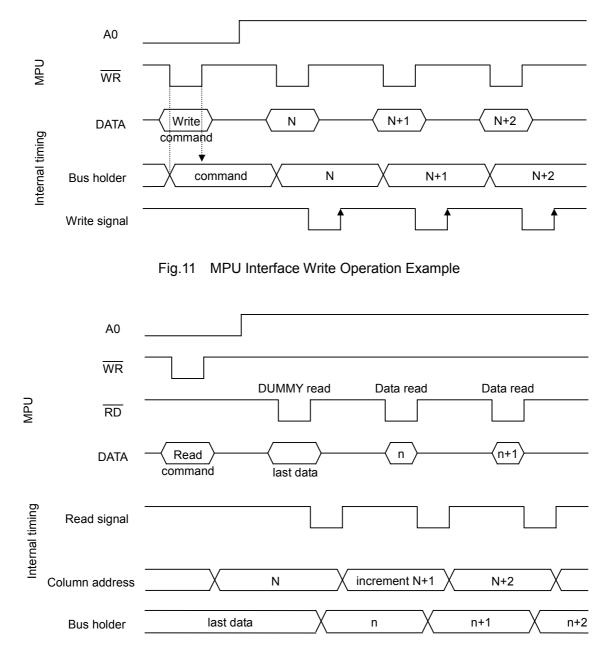

| •. | 6.1          | MPU Interface                                                                                                         | -  |  |  |  |  |

|    | ••••         | 6.1.1 MPU Interface Selection                                                                                         |    |  |  |  |  |

|    |              | 6.1.2 Parallel MPU Interface                                                                                          | 18 |  |  |  |  |

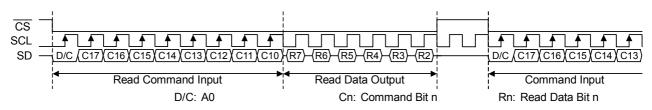

|    |              | 6.1.3 Serial Interface                                                                                                | 19 |  |  |  |  |

|    |              | 6.1.4 Internal Data Bus Expansion of Display Data                                                                     |    |  |  |  |  |

|    |              | 6.1.5 Access to Display Data RAM and Internal Register via MPU Interface                                              |    |  |  |  |  |

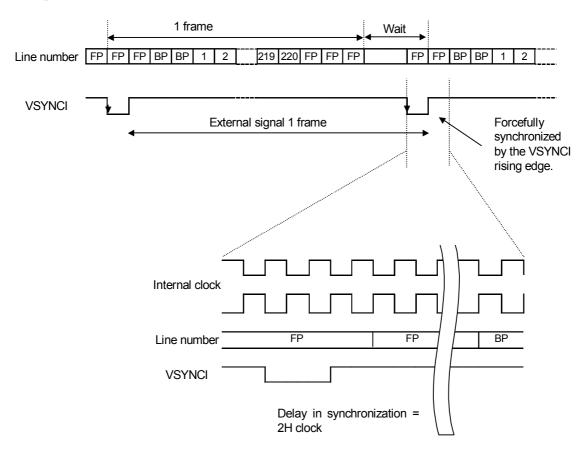

|    |              | 6.1.6 VSYNC Interface                                                                                                 |    |  |  |  |  |

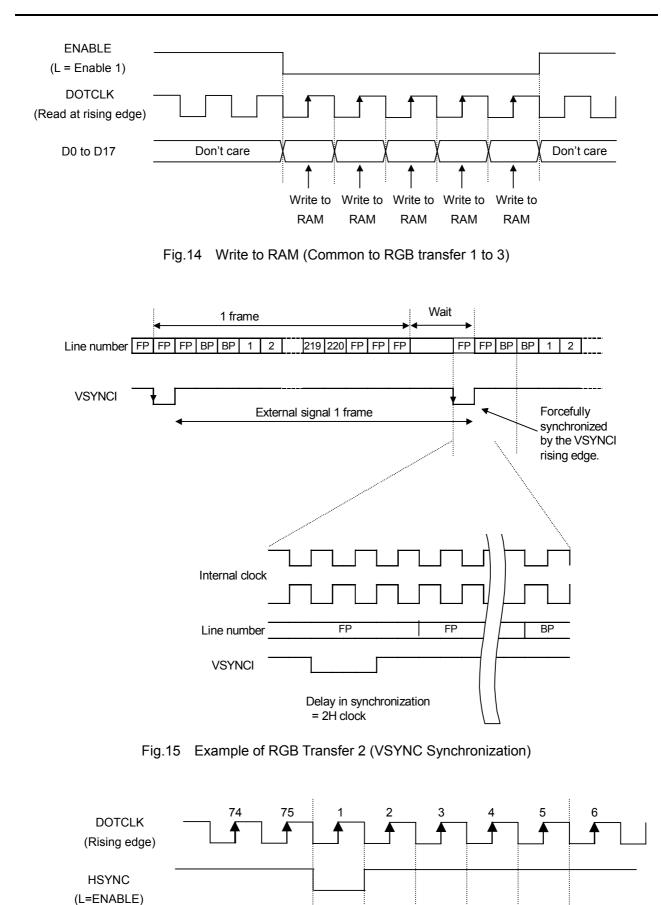

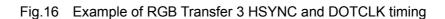

|    | 6.2          | RGB Interface                                                                                                         | -  |  |  |  |  |

|    |              | 6.2.1 RGB Interface Selection                                                                                         |    |  |  |  |  |

|    |              | <ul><li>6.2.2 RGB Interface Operation Modes</li><li>6.2.3 Internal Data Bus of RGB Interface</li></ul>                |    |  |  |  |  |

|    |              | <ul><li>6.2.3 Internal Data Bus of RGB Interface</li><li>6.2.4 Access to Display Data RAM via RGB Interface</li></ul> |    |  |  |  |  |

|    | 6.3          | Write Speed to Display Data RAM                                                                                       |    |  |  |  |  |

|    | 6.4          | Display Data RAM                                                                                                      |    |  |  |  |  |

|    | ••••         | 6.4.1 Display Data RAM                                                                                                |    |  |  |  |  |

|    |              | 6.4.2 Source Line Drive Output Pins and RAM Data                                                                      |    |  |  |  |  |

|    |              | 6.4.3 Row Address Circuit/Column Address Circuit                                                                      |    |  |  |  |  |

|    |              | 6.4.4 Area Scrolling                                                                                                  | 36 |  |  |  |  |

|    |              | 6.4.5 Partial Display                                                                                                 |    |  |  |  |  |

|    |              | 6.4.6 AC Operation Drive                                                                                              |    |  |  |  |  |

|    | 6.5          | Oscillation Circuit                                                                                                   |    |  |  |  |  |

|    | 6.6          | Setting Gate Line Scan Mode                                                                                           |    |  |  |  |  |

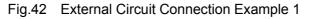

|    | 6.7          | How to Connect to the External Power Supply                                                                           | 42 |  |  |  |  |

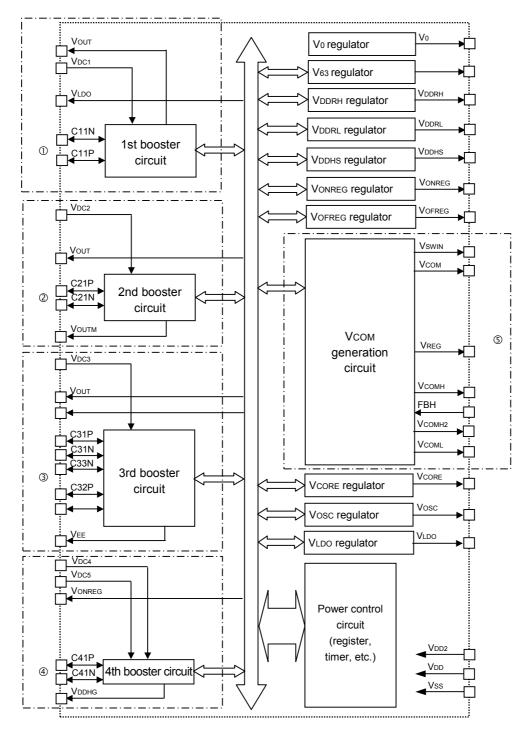

|     | 6.8  | Description of Operation of Built-in Power Supply                          | 45  |

|-----|------|----------------------------------------------------------------------------|-----|

|     | 6.9  | Power Supply for LCD and Main Specifications for Power Supply              | 46  |

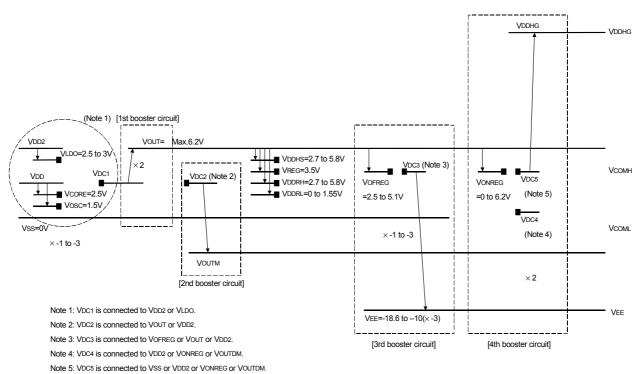

|     |      | 6.9.1 Basic Configuration Diagram of Built-in Power Supply                 | 47  |

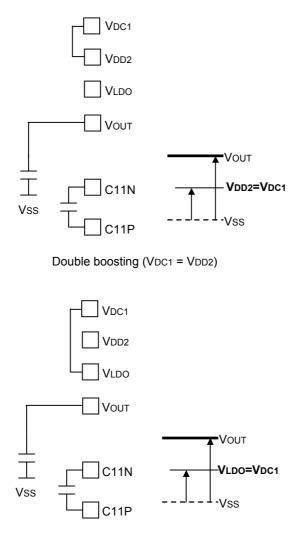

|     |      | 6.9.2 The 1st Booster Circuit                                              | 48  |

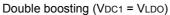

|     |      | 6.9.3 The 2nd Booster Circuit                                              | 49  |

|     |      | 6.9.4 The 3rd Booster Circuit                                              | 50  |

|     |      | 6.9.5 The 4th Booster Circuit                                              |     |

|     |      | 6.9.6 Vcoм Generation Circuit                                              | 53  |

|     | 6.10 | Connection Diagram of External Parts                                       | 54  |

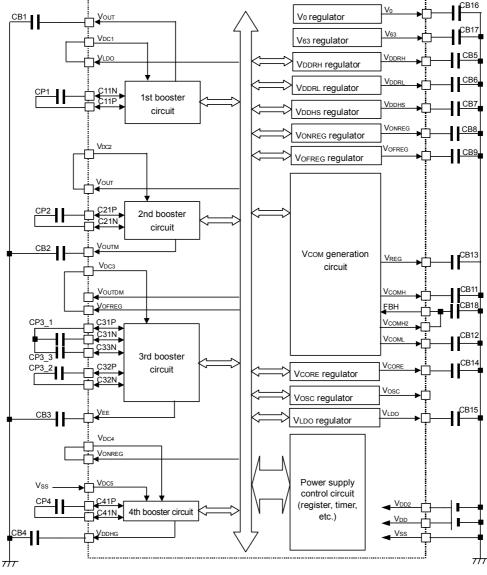

|     | 6.11 | Gray scale Voltage Generation Circuit                                      |     |

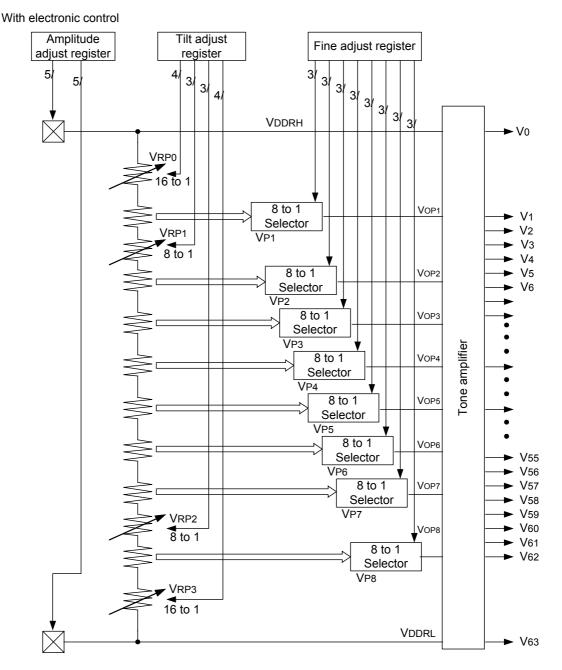

|     |      | 6.11.1 Adjusting Gray Scale Voltage                                        |     |

|     |      | 6.11.2 Amplitude Adjustment                                                |     |

|     |      | 6.11.3 Tilt Adjustment                                                     |     |

|     |      | 6.11.4 Fine Adjustment of Gray Scale Voltage                               |     |

|     |      | Calculation of Gray Scale Voltage                                          |     |

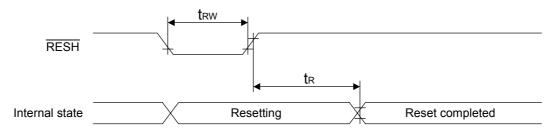

|     | 6.13 | Resetting                                                                  | 64  |

| 7.  | COM  | IMANDS                                                                     | 65  |

|     | 7.1  | Command List                                                               |     |

|     | 7.2  | Initial Values of a Single-Byte Command                                    | 67  |

|     | 7.3  | Parameter Initial Value List                                               | 68  |

|     | 7.4  | Explanation of Commands                                                    | 70  |

|     | 7.5  | Instruction Setup Example (Reference)                                      |     |

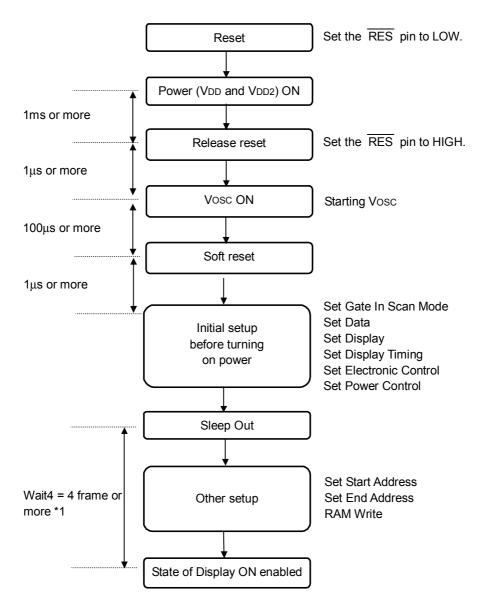

|     |      | 7.5.1 Initial Setup to Display-ON (VCORE forceful ON, VCORE forceful OFF)  |     |

|     |      | 7.5.2 Initial Setup to Display-ON (Normal use of VCORE)                    |     |

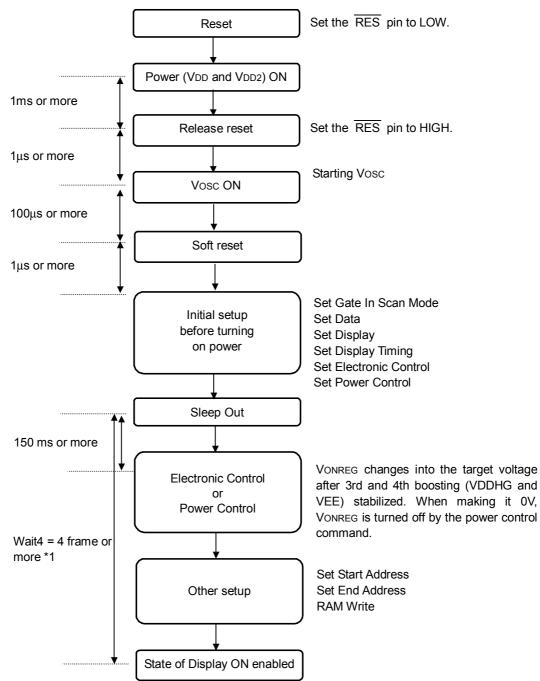

|     |      | 7.5.3 Power OFF Sequence                                                   |     |

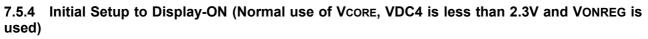

|     |      | 7.5.4 Initial Setup to Display-ON (Normal use of , VDC4 is less than 2.3V) |     |

|     |      | 7.5.5 Power OFF sequence                                                   | 103 |

| 8.  | ABS  | OLUTE MAXIMUM RATINGS                                                      | 104 |

| 9.  | REC  | OMMENDED OPERATING CONDITIONS                                              | 105 |

| 10. | DC C | CHARACTERISTICS                                                            | 106 |

| 11. | AC C | CHARACTERISTICS                                                            |     |

|     |      | Oscillation Frequency                                                      |     |

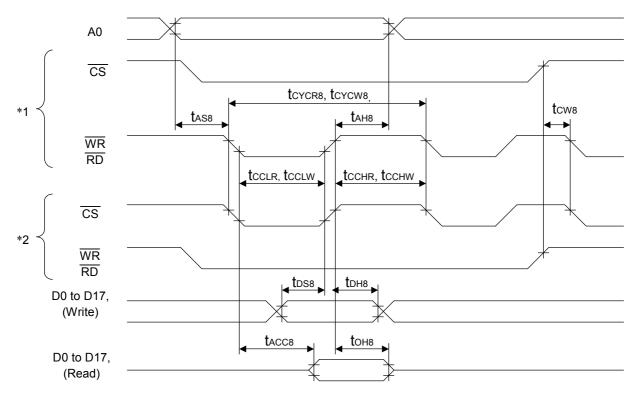

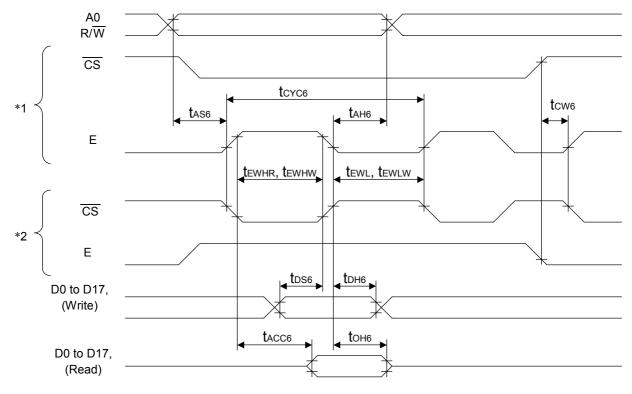

|     |      | Parallel Interface                                                         |     |

|     |      | 11.2.1 The 80-Series MPUs                                                  |     |

|     |      | 11.2.2 The 68-Series MPUs                                                  |     |

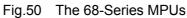

|     | 11.3 | Serial Interface                                                           |     |

|     |      | Resetting                                                                  |     |

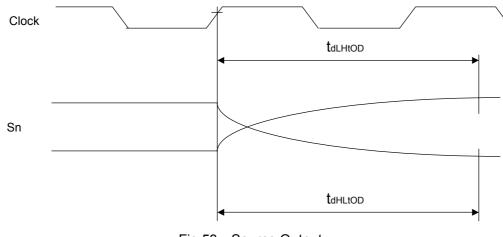

|     |      | Source Output                                                              |     |

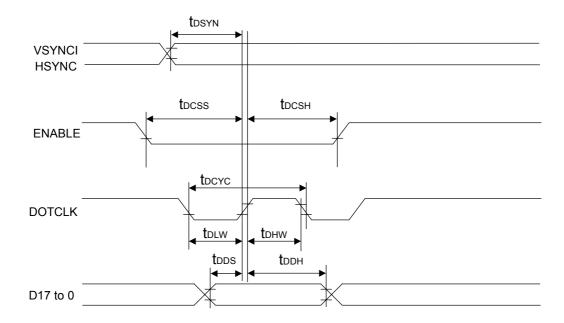

|     |      | RGB Interface                                                              |     |

| 12. | NOT  |                                                                            | 114 |

# 1. **DESCRIPTION**

The S1D19105 series is a 1-chip driver for driving amorphous Si-TFT with built-in data RAM that contains 176 RGB  $\times$  220 dots, supporting 262k-color display. Since this series contains all power circuits necessary for the 220-output gate driver, 176-RGB output source driver, and the display, the TFT color panel module of a maximum of 176 RGB  $\times$  220 dots can be constructed with a minimum of components.

The S1D19105 incorporates 8/9/16/18-bit parallel interface that can be directly attached to the micro computer (hereafter referred to as MPU) bus. The 3-line serial interface can also be used. The S1D19105 series receives parallel or serial display data from the microprocessor, stores it in the display data RAM, and outputs resource line drive signals, gate driver drive signals, and AC operation timing signals independent from MPU operations. Also, for movie display, 6/16/18-bit RGB interface and VSYNC synchronization function are provided.

The S1D19105 series has the low current consumption, source line drive circuit (including reference voltage adjustment resistor and bias circuit for reference voltage circuit), high-efficiency power circuit and the CR oscillation circuit for fully-built-in display clock that does not require external parts. In addition, power can be controlled more finely using command control, as this series supports 8-color display mode and partial display mode. The S1D19105 series provides a high-performance but handy display system with a minimum of components in the minimum power consumption.

# 2. FEATURES

- Supports 176 RGB × 220 dots and 262,144 colors amorphous Si-TFT color panel.

- RAM capacity  $176 \times 3 \times 220 \times 6 = 696,960$  bits

- Display function

Display of 262k-color at a time

Area scrolling

Partial display

8-color display mode

• Interface function

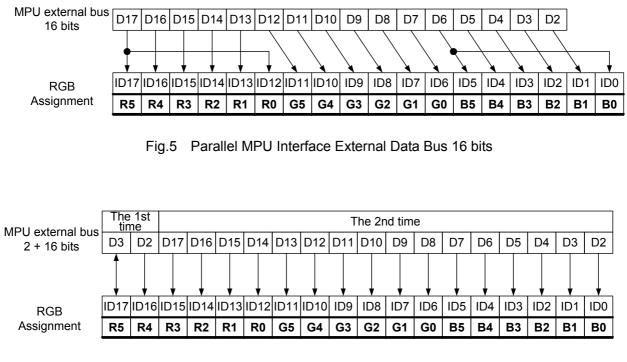

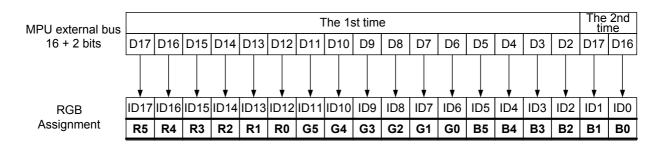

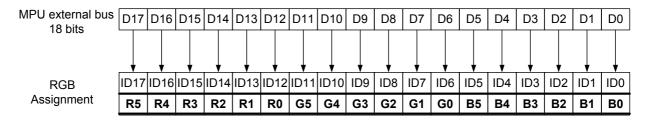

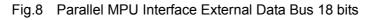

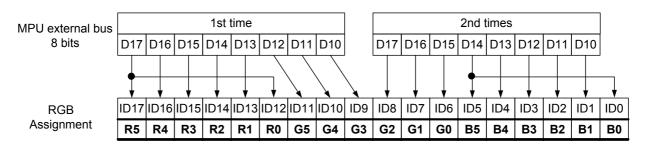

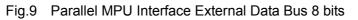

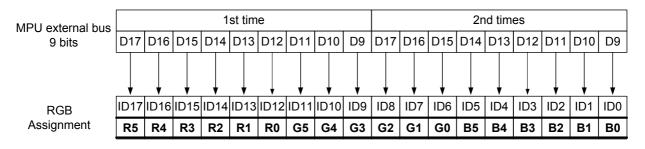

Selection from 8/9/16/18-bit parallel MPU interface. Direct attachment to either of 80- and 68-series MPUs.

262k-color display via 16-bit interface by selecting 2+16 and 16+2 modes.

Serial interface 3 signal lines ( $\overline{CS}$ , SCL, and SI signals)

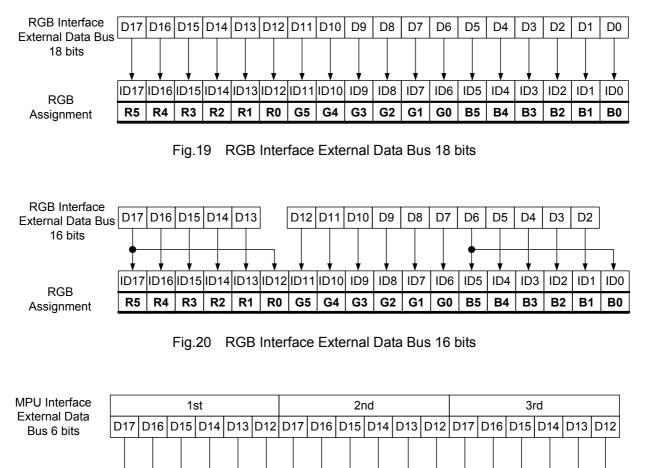

Selection from 6/16/18-bit RGB interface specifically for moving picture display, etc.

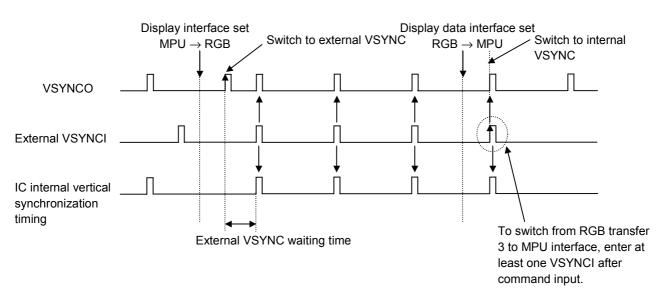

VSYNC synchronization function provides flicker-free moving picture display.

- $176 \times 3$  source line drive output A 6-bit D/A converter is included.

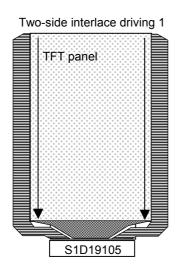

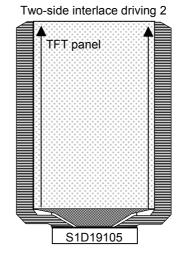

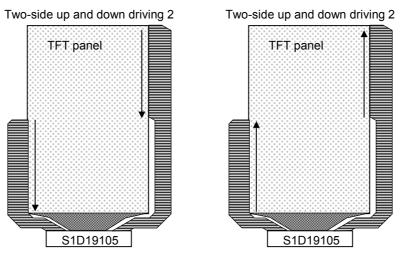

- A 110 output each is placed on the right and left sides of the 220 gate line drive output chip. Also, supports interlace drive.

- CR oscillation circuit (External clocks can also be used.)

- Common electrode drive signal outputs (VCOM signals)

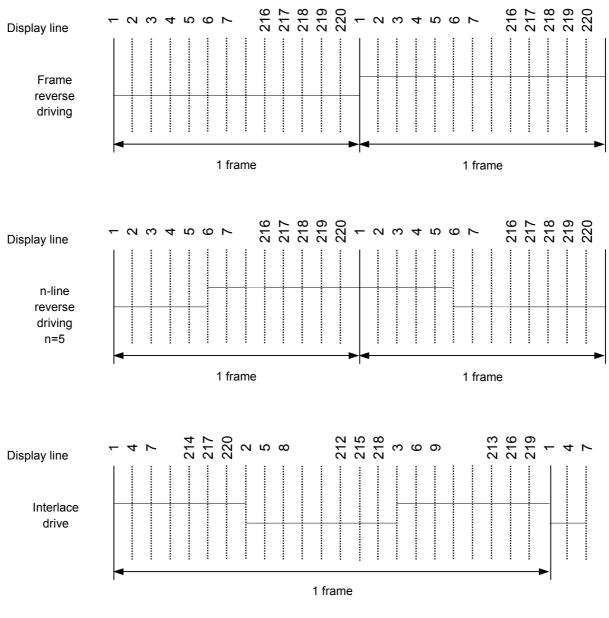

Allows 1-frame/3-line interlace/n-line reverse driving.

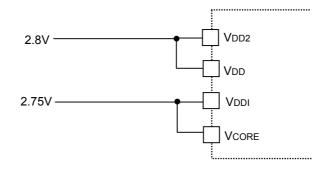

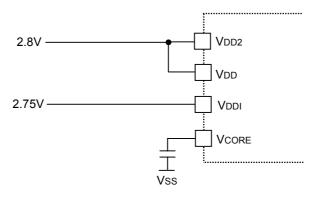

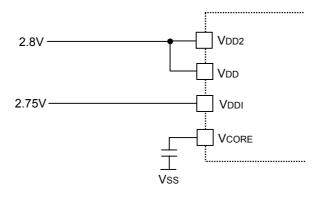

- Low supply voltage operation

- VDDI VSS = 1.65 to 3.3V (interface I/O power supply)

VDD - VSS = 2.3 to 3.1V (power supply for internal logic power supply)

VDD2 - VSS = 2.3 to 3.1V (power supply for built-in power circuits)

VDDCORE - VSS = 2.3 to 3.1V (internal logic power supply)

Source voltage = Max.5.5V

Gate voltage = Max.30V

- BUMP layout appropriate for COG assembly

- Package models available: Au bump chip and COF

#### 3. **BLOCK DIAGRAM** /com G110 G220 S528 G111 S. • <u>υ</u>. •• GD1 to 4 Gate driver Gate driver ά VOUT < VDC1 VDD Source driver VLD0 -H VDDI C11N - Vdd2 C11P < Display data latch circuit VDC2 – Vss C12N < Display timing generator VREG C12P VDDHS VOUTM · Row address Line address I/O buffer VDC3 VONREG Display data RAM C31N · 176x3x220x6 VOFREG Power circuit/ $\gamma$ correction circuit C31P < VCORE C33N -C32N Vosc C32P VLDO VEE · Column address VDC4 VDC5 C41N -C41P -VDDHG < OSCI **V**сом Oscillation circuit - osco Vswin < Control logic CWN CWP Vcomw · FBW **V**сомн <sup>-</sup> FBH VCOMH2 1 VCOML TEST1 to 5 **RGB** interface System interface 5 VDDRH VDDRL V1 to V8 to D17 WR ₩ RD + + IF1 to 3\_ C86\_ V63 -VSYNCO-HSYNCŝ VSYNCI-/SYNCO2--OSCO--ISCI-RESŝ ENABLE SCL DOTCLK(DCK) â Fig.1 S1D19105 Series Block Diagram

### S1D19105 Series (Rev.1.1)

#### 4. **PIN ASSIGNMENT**

#### S1D19105 Specifications of Chip 4.1

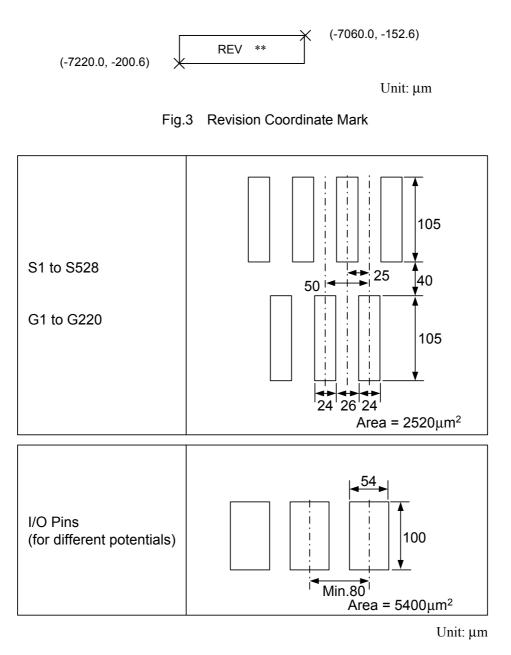

|                | Parameter     | Dimer | Unit |      |

|----------------|---------------|-------|------|------|

|                | Falameter     | X     | Y    | Omit |

| Chip size      |               | 19.56 | 2.49 | mm   |

| Chip thickness |               | 400   |      | μm   |

| Bump pitch     |               | Min   | .50  | μm   |

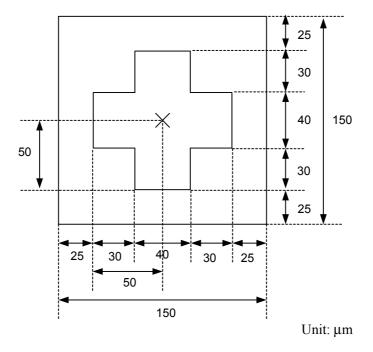

| Bump size      | No.1 to 205   | 54    | 100  | μm   |

|                | No.206 to 978 | 24    | 105  | μm   |

| Bump height    |               | Тур   | .15  | μm   |

| Table 1 | Specifications | of Chip |

|---------|----------------|---------|

|---------|----------------|---------|

Note: These values are given for reference only.

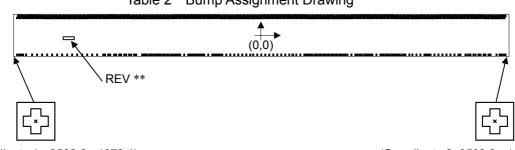

(Coordinate 1: -9593.0, -1079.1)

(Coordinate 2: 9593.0, -1079.1)

The alignment mark is put on two locations.

Fig.2 Alignment Mark

Fig.4 Bump Size and Assignment Drawing

г

# 4.2 Bump Center Coordinates

| BUMP No. | Signal name | Х       | Y       |

|----------|-------------|---------|---------|

| 1        | ADUMMY      | -9429.2 | -1098.6 |

| 2        | BDUMMY      | -9349.2 |         |

| 3        | DUMMY       | -9269.2 |         |

| 4        | Vсом        | -9189.2 |         |

| 5        | Vсом        | -9109.2 |         |

| 6        | DUMMY       | -9029.2 |         |

| 7        | Vddhg       | -8949.2 |         |

| 8        | Vddhg       | -8869.2 |         |

| 9        | DUMMY       | -8789.2 |         |

| 10       | C41P        | -8709.2 |         |

| 11       | C41P        | -8629.2 |         |

| 12       | DUMMY       | -8549.2 |         |

| 13       | C41N        | -8469.2 |         |

| 14       | C41N        | -8389.2 |         |

| 15       | DUMMY       | -8309.2 |         |

| 16       | Vonreg      | -8229.2 |         |

| 17       | VDC4        | -8149.2 |         |

| 18       | VDC5        | -8039.2 |         |

| 19       | Vofreg      | -7929.2 |         |

| 20       | VDC3        | -7819.2 |         |

| 21       | VOUTDM      | -7739.2 |         |

| 22       | C32P        | -7649.2 |         |

| 23       | C32P        | -7569.2 |         |

| 24       | C32N        | -7435.5 |         |

| 25       | C32N        | -7355.5 |         |

| 26       | DUMMY       | -7275.5 |         |

| 27       | VEE         | -7195.5 |         |

| 28       | VEE         | -7115.5 |         |

| 29       | C33N        | -7025.5 |         |

| 30       | C33N        | -6945.5 |         |

| 31       | DUMMY       | -6865.5 |         |

| 32       | C31N        | -6785.5 |         |

| 33       | C31N        | -6705.5 |         |

| 34       | C31P        | -6571.8 |         |

| 35       | C31P        | -6491.8 | ↓       |

Table 3 Bump Center Coordinates

<u>Unit: μm</u>

| Unit: µ  |             |         |         |  |

|----------|-------------|---------|---------|--|

| BUMP No. | Signal name | X       | Y       |  |

| 36       | VCORE       | -6411.8 | -1098.6 |  |

| 37       | VCORE       | -6331.8 |         |  |

| 38       | VCORE       | -6251.8 |         |  |

| 39       | VCORE       | -6171.8 |         |  |

| 40       | Vddi        | -6091.8 |         |  |

| 41       | Vddi        | -6011.8 |         |  |

| 42       | Vss         | -5931.8 |         |  |

| 43       | Vss         | -5851.8 |         |  |

| 44       | Vss         | -5771.8 |         |  |

| 45       | Vss         | -5691.8 |         |  |

| 46       | C86         | -5611.8 |         |  |

| 47       | IF1         | -5531.8 |         |  |

| 48       | IF2         | -5451.8 |         |  |

| 49       | IF3         | -5371.8 |         |  |

| 50       | DUMMY       | -5291.8 |         |  |

| 51       | V63         | -5211.8 |         |  |

| 52       | V8          | -5131.8 |         |  |

| 53       | V7          | -5051.8 |         |  |

| 54       | V6          | -4971.8 |         |  |

| 55       | V5          | -4891.8 |         |  |

| 56       | V4          | -4811.8 |         |  |

| 57       | V3          | -4731.8 |         |  |

| 58       | V2          | -4651.8 |         |  |

| 59       | V1          | -4571.8 |         |  |

| 60       | V0          | -4491.8 |         |  |

| 61       | DUMMY       | -4411.8 |         |  |

| 62       | RES         | -4331.8 |         |  |

| 63       | DUMMY       | -4251.8 |         |  |

| 64       | CS          | -4171.8 |         |  |

| 65       | DUMMY       | -4091.8 |         |  |

| 66       | A0          | -4011.8 |         |  |

| 67       | DUMMY       | -3931.8 |         |  |

| 68       | WR          | -3851.8 |         |  |

| 69       | DUMMY       | -3771.8 |         |  |

| 70       | RD          | -3691.8 | ♦       |  |

|          |             |         |         |  |

| BUMP No. | Signal name | Х       | Y       |

|----------|-------------|---------|---------|

| 71       | DUMMY       | -3611.8 | -1098.6 |

| 72       | D0          | -3531.8 |         |

| 73       | D1          | -3371.8 |         |

| 74       | D2          | -3211.8 |         |

| 75       | D3          | -3051.8 |         |

| 76       | D4          | -2891.8 |         |

| 77       | D5          | -2731.8 |         |

| 78       | D6          | -2571.8 |         |

| 79       | D7          | -2411.8 |         |

| 80       | D8          | -2251.8 |         |

| 81       | D9          | -2091.8 |         |

| 82       | D10         | -1931.8 |         |

| 83       | D11         | -1771.8 |         |

| 84       | D12         | -1611.8 |         |

| 85       | D13         | -1451.8 |         |

| 86       | D14         | -1291.8 |         |

| 87       | D15         | -1131.8 |         |

| 88       | D16         | -971.8  |         |

| 89       | D17         | -811.8  |         |

| 90       | DUMMY       | -651.8  |         |

| 91       | VSYNCO2     | -491.8  |         |

| 92       | VSYNCO      | -331.8  |         |

| 93       | VSYNCI      | -171.8  |         |

| 94       | DUMMY       | -91.8   |         |

| 95       | HSYNC       | -11.8   |         |

| 96       | DUMMY       | 68.2    |         |

| 97       | DCK         | 148.2   |         |

| 98       | DUMMY       | 228.2   |         |

| 99       | ENABLE      | 308.2   |         |

| 100      | DUMMY       | 388.2   |         |

| 101      | DUMMY       | 468.2   |         |

| 102      | DUMMY       | 548.2   |         |

| 103      | DUMMY       | 628.2   |         |

| 104      | SCL         | 708.2   |         |

| 105      | DUMMY       | 788.2   | •       |

| BUMP No.         Signal name         X         Y           106         SD         868.2         -1098.6           107         EECK         1028.2         □           108         EEDA         1188.2         □         □           109         EECS         1348.2         □         □           110         VEP         1508.2         □         □           111         TEST1         1668.2         □         □           111         DUMMY         1748.2         □         □           113         TEST2         1828.2         □         □           114         DUMMY         1908.2         □         □           115         TEST3         1988.2         □         □           116         DUMMY         2068.2         □         □           116         DUMMY         2282.2         □         □           118         DUMMY         2388.2         □         □           120         DUMMY         2388.2         □         □           121         TRI         2468.2         □         □           122         OSCO         2548.2         □                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |             |        | Unit: µı |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|--------|----------|

| 107       EECK       1028.2       1         108       EEDA       1188.2       1         109       EECS       1348.2       1         110       VEP       1508.2       1         111       TEST1       1668.2       1         111       TEST1       1668.2       1         111       TEST2       1828.2       1         113       TEST2       1828.2       1         114       DUMMY       1908.2       1         115       TEST3       1988.2       1         116       DUMMY       2068.2       1         117       TEST4       2148.2       1         118       DUMMY       2288.2       1         119       TEST5       2308.2       1         120       DUMMY       2388.2       1         121       TRI       2468.2       1         122       OSCO       2548.2       1         123       OSCI       2628.2       1         124       Vosc       2708.2       1         125       VDDRL       2798.2       1         126       VDDRH       2908.2       1 </td <td>BUMP No.</td> <td>Signal name</td> <td>Х</td> <td>Y</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BUMP No. | Signal name | Х      | Y        |

| 108       EEDA       1188.2       Image: style sty | 106      | SD          | 868.2  | -1098.6  |

| 109         EECS         1348.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107      | EECK        | 1028.2 |          |

| 110         VEP         1508.2         I           111         TEST1         1668.2         I           112         DUMMY         1748.2         I           113         TEST2         1828.2         I           114         DUMMY         1908.2         I           115         TEST3         1988.2         I           116         DUMMY         2068.2         I           117         TEST4         2148.2         I           118         DUMMY         2288.2         I           119         TEST5         2308.2         I           120         DUMMY         2388.2         I           121         TRI         2468.2         I           122         OSCO         2548.2         I           123         OSCI         2628.2         I           124         Vosc         2708.2         I           125         VDDRL         2798.2         I           126         VDDRH         2908.2         I           128         VSS         3088.2         I           130         VSS         3248.2         I           133 <td< td=""><td>108</td><td>EEDA</td><td>1188.2</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 108      | EEDA        | 1188.2 |          |

| 111         TEST1         1668.2           112         DUMMY         1748.2           113         TEST2         1828.2           114         DUMMY         1908.2           115         TEST3         1988.2           116         DUMMY         2068.2           117         TEST4         2148.2           118         DUMMY         2228.2           119         TEST5         2308.2           120         DUMMY         2388.2           121         TRI         2468.2           122         OSCO         2548.2           123         OSCI         2628.2           124         Vosc         2708.2           125         VDRL         2798.2           126         VDDRH         2908.2           127         VREG         2998.2           128         VSS         3068.2           130         VSS         3248.2           131         VSS         3328.2           132         VSS         3468.2           133         VSS         3488.2           134         VSS         3568.2           135         VSS <td< td=""><td>109</td><td>EECS</td><td>1348.2</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 109      | EECS        | 1348.2 |          |

| 112       DUMMY       1748.2       Image: style="text-align: center;">Image: style="text-align: center;">Image: style="text-align: style="text-aligo: style="text-align: style="text-align: style="text-al | 110      | VEP         | 1508.2 |          |

| 113       TEST2       1828.2         114       DUMMY       1908.2         115       TEST3       1988.2         116       DUMMY       2068.2         117       TEST4       2148.2         118       DUMMY       228.2         119       TEST5       2308.2         120       DUMMY       2388.2         121       TRI       2468.2         122       OSCO       2548.2         123       OSCI       2628.2         124       Vosc       2708.2         125       VDDRL       2798.2         126       VDDRH       2908.2         127       VREG       2998.2         128       VSS       3088.2         130       VSS       3248.2         131       VSS       3328.2         132       VSS       348.2         133       VSS       348.2         134       VSS       3568.2         135       VSS       3648.2         136       VDDI       3728.2         137       VDDI       3808.2         138       VDDI       3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111      | TEST1       | 1668.2 |          |

| 114       DUMMY       1908.2         115       TEST3       1988.2         116       DUMMY       2068.2         117       TEST4       2148.2         118       DUMMY       2228.2         119       TEST5       2308.2         120       DUMMY       2388.2         121       TRI       2468.2         122       OSCO       2548.2         123       OSCI       2628.2         124       Vosc       2708.2         125       VDDRL       2798.2         126       VDDRH       2908.2         127       VREG       2998.2         128       VSS       3088.2         129       VSS       3168.2         130       VSS       3248.2         131       VSS       3328.2         132       VSS       3408.2         133       VSS       3488.2         134       VSS       3568.2         135       VSS       3648.2         136       VDDI       3728.2         137       VDDI       3808.2         138       VDDI       3868.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 112      | DUMMY       | 1748.2 |          |

| 115         TEST3         1988.2           116         DUMMY         2068.2           117         TEST4         2148.2           118         DUMMY         2228.2           119         TEST5         2308.2           120         DUMMY         2388.2           121         TRI         2468.2           122         OSCO         2548.2           123         OSCI         2628.2           124         Vosc         2708.2           125         VDDRL         2798.2           126         VDDRH         2908.2           127         VREG         2998.2           128         VSS         3088.2           130         VSS         3248.2           131         VSS         3328.2           132         VSS         3408.2           133         VSS         3488.2           133         VSS         3648.2           134         VSS         3568.2           135         VSS         3648.2           136         VDDI         3728.2           137         VDDI         3808.2           138         VDDI         380                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113      | TEST2       | 1828.2 |          |

| 116       DUMMY       2068.2       Image: scalar stress in the stress  | 114      | DUMMY       | 1908.2 |          |

| 117       TEST4       2148.2       118         118       DUMMY       2228.2       119         119       TEST5       2308.2       120         120       DUMMY       2388.2       121         121       TRI       2468.2       121         122       OSCO       2548.2       123         123       OSCI       2628.2       121         124       Vosc       2708.2       121         125       VDDRL       2798.2       121         126       VDDRH       2908.2       121         127       VREG       2998.2       121         128       VSS       3088.2       121         130       VSS       3248.2       121         131       VSS       3328.2       121         132       VSS       3408.2       121         133       VSS       3488.2       121         134       VSS       3568.2       132         135       VSS       3648.2       136         136       VDI       3728.2       133         138       VDI       3888.2       133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 115      | TEST3       | 1988.2 |          |

| 118       DUMMY       2228.2       Image: scalar stress in the stress  | 116      | DUMMY       | 2068.2 |          |

| 119       TEST5       2308.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 117      | TEST4       | 2148.2 |          |

| 120       DUMMY       2388.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 118      | DUMMY       | 2228.2 |          |

| 121       TRI       2468.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 119      | TEST5       | 2308.2 |          |

| 122       OSCO       2548.2          123       OSCI       2628.2          124       VOSC       2708.2          125       VDDRL       2798.2          126       VDDRH       2908.2          127       VREG       2998.2          128       Vss       3088.2          130       Vss       3248.2          131       Vss       3328.2          133       Vss       3408.2          134       Vss       3568.2          135       Vss       3648.2          137       VDI       3808.2          138       VDI       3888.2          139       VDI       3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120      | DUMMY       | 2388.2 |          |

| 123       OSCI       2628.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 121      | TRI         | 2468.2 |          |

| 124       Vosc       2708.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 122      | OSCO        | 2548.2 |          |

| 125       VDDRL       2798.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 123      | OSCI        | 2628.2 |          |

| 126       VDDRH       2908.2         127       VREG       2998.2         128       VSS       3088.2         129       VSS       3168.2         130       VSS       3248.2         131       VSS       3328.2         132       VSS       3408.2         133       VSS       3488.2         134       VSS       3568.2         135       VSS       3648.2         136       VDDI       3728.2         137       VDDI       3808.2         138       VDDI       3808.2         139       VDDI       3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 124      | Vosc        | 2708.2 |          |

| 127       VREG       2998.2         128       Vss       3088.2         129       Vss       3168.2         130       Vss       3248.2         131       Vss       3328.2         132       Vss       3408.2         133       Vss       3488.2         134       Vss       3568.2         135       Vss       3648.2         136       VDI       3728.2         137       VDI       3808.2         138       VDI       3888.2         139       VDI       3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 125      | Vddrl       | 2798.2 |          |

| 128       Vss       3088.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 126      | Vddrh       | 2908.2 |          |

| 129       Vss       3168.2          130       Vss       3248.2          131       Vss       3328.2          132       Vss       3408.2          133       Vss       3488.2          134       Vss       3568.2          136       VDI       3728.2          137       VDI       3808.2          138       VDI       3888.2          139       VDI       3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 127      | VREG        | 2998.2 |          |

| 130       Vss       3248.2         131       Vss       3328.2         132       Vss       3408.2         133       Vss       3488.2         134       Vss       3568.2         135       Vss       3648.2         136       VDI       3728.2         137       VDI       3808.2         138       VDI       3808.2         139       VDI       3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 128      | Vss         | 3088.2 |          |

| 131       Vss       3328.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 129      | Vss         | 3168.2 |          |

| 132       Vss       3408.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 130      | Vss         | 3248.2 |          |

| 133       Vss       3488.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 131      | Vss         | 3328.2 |          |

| 134         Vss         3568.2            135         Vss         3648.2            136         VDDI         3728.2            137         VDDI         3808.2            138         VDDI         3888.2            139         VDDI         3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132      | Vss         | 3408.2 |          |

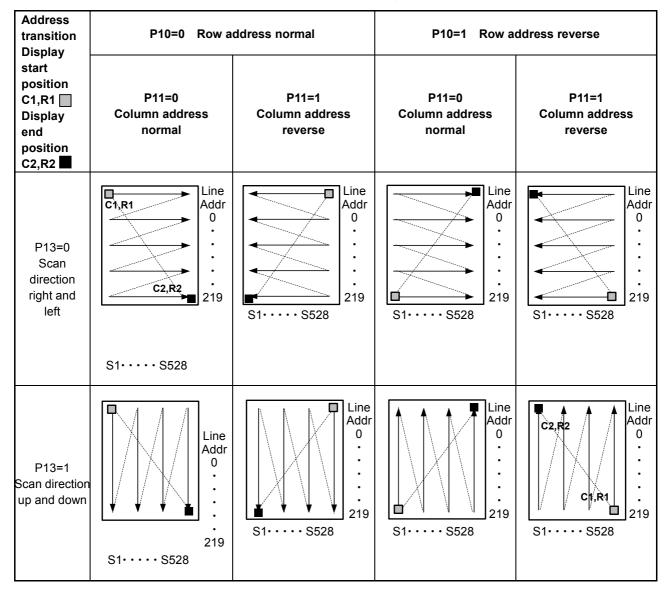

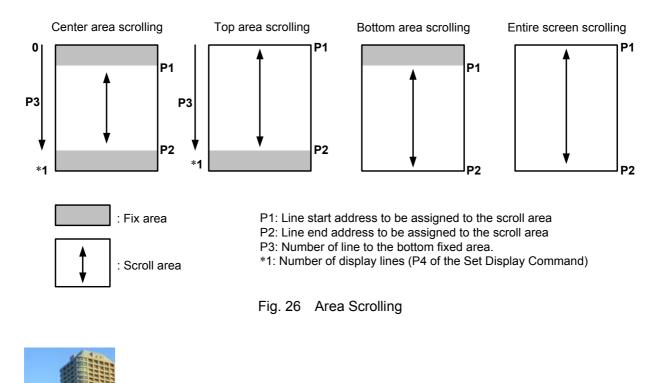

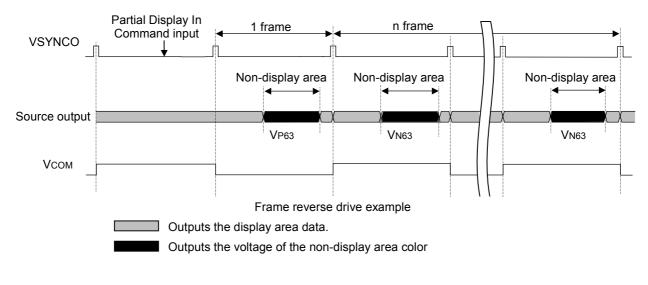

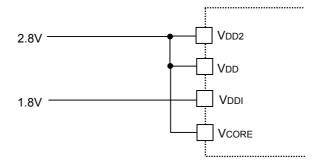

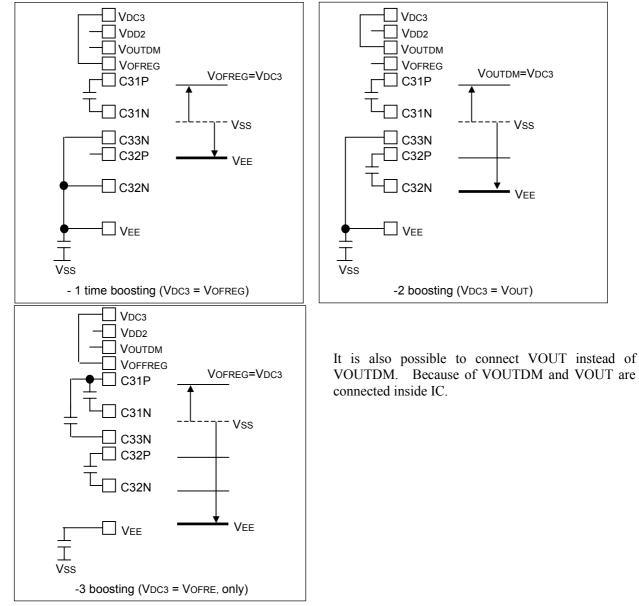

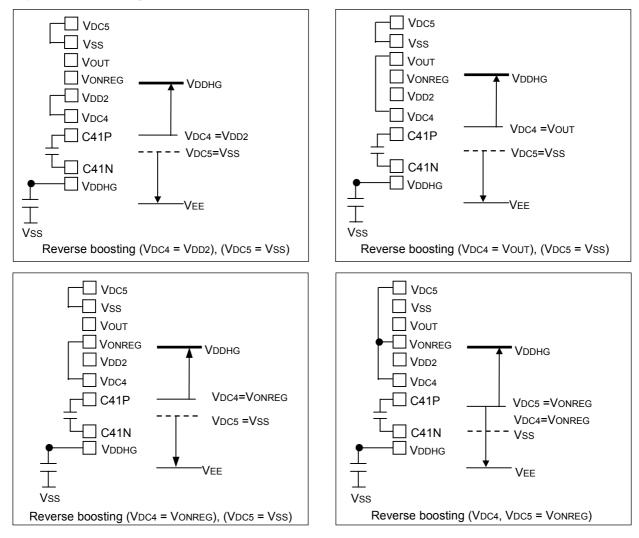

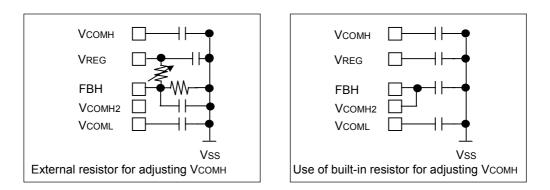

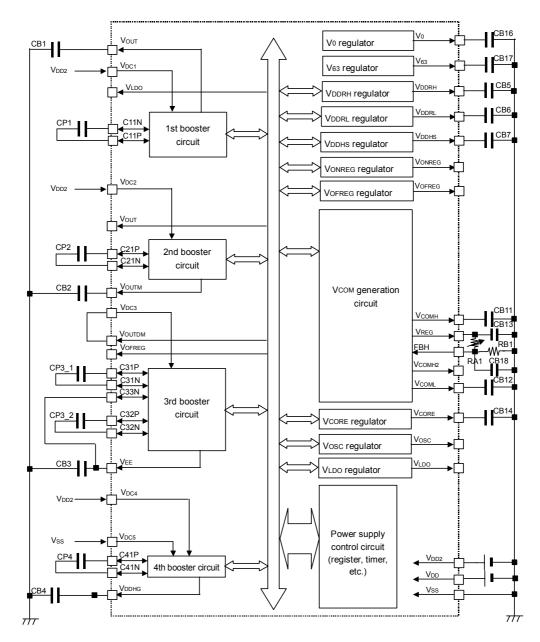

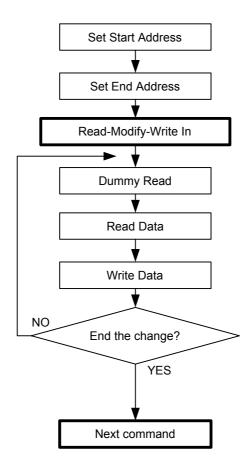

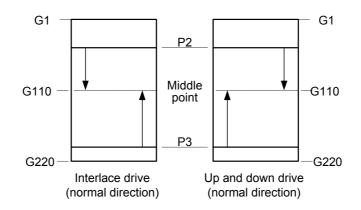

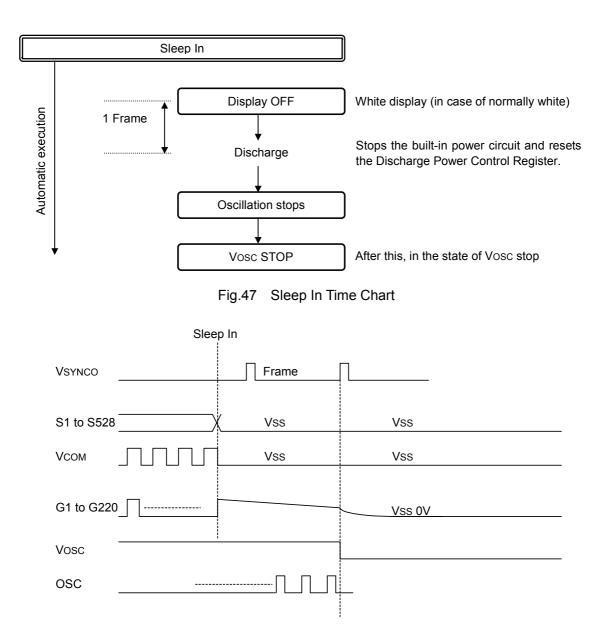

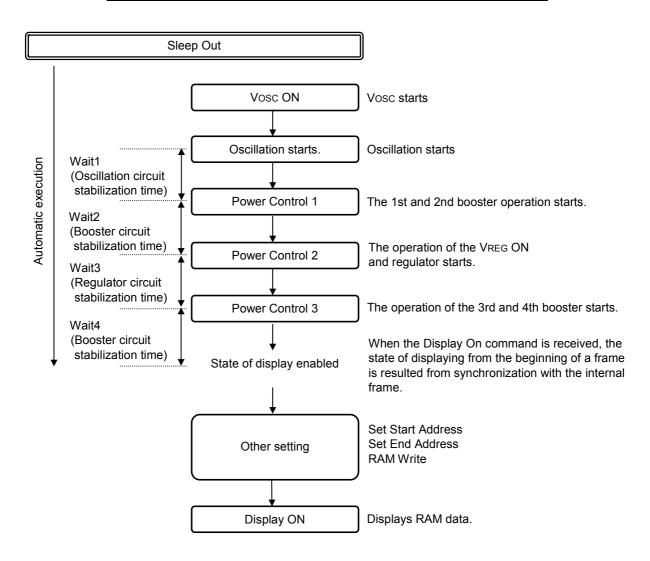

| 135         Vss         3648.2           136         VDDI         3728.2           137         VDDI         3808.2           138         VDDI         3888.2           139         VDDI         3968.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 133      | Vss         | 3488.2 |          |